What is a FIFO in an FPGA

HTML-код

- Опубликовано: 30 сен 2024

- NEW! Buy my book, the best FPGA book for beginners: nandland.com/b...

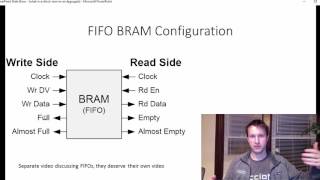

Learn how FIFOs work inside FPGAs. FIFO is First In First Out. They're very useful, especially for buffering up data and crossing clock domains inside of your VHDL or Verilog design.

Here's my example for Register-based FIFO in VHDL:

www.nandland.c...

Please support this channel! Buy a Go Board today! You can use this board to test out the FIFO concepts in this video. Your support allows me to make more of these videos, so thank you!

www.nandland.c...

Like my content? Help me make more at Patreon!

/ nandland

Thank you, man. I really appreciate your videos, I'm gonna graduate with them :D

Support this channel! Buy a Go Board today! www.nandland.com/goboard/introduction.html

why is it that we can read with only 50% efficiency? What if we simply check that if the fifo is empty or not and in the same clock cycle we perform a read operation?

Thanks for the informative video! Although I gotta say I really miss your previous format - as in theory followed by practical example. For me following practical examples is the easiest way to really understand how to use different things available in FPGA.

asmi06 thanks for the feedback! I'll keep that in mind for future videos. It's a balance between teaching a concept well and keeping the video short. I feel like if I did too many examples it might be too long. Thoughts?

For me video can be as long as it needs to be - provided that it maintains focus on the topic at hand without straying too much from it. I regularly watch 1+ hr long videos - as a matter of fact, most "training" kind of videos are that long as they cover topic in great detail.

So I'm not sure how others feel about this, but I tend to prefer longer videos exactly because they usually cover subject in greater detail.

+asmi06 ok I hear you. Those take longer too, so I can do less of them. What about if I revisited this topic with a video all about creating the VHDL and Verilog for FIFOs? Think concept in one, example in another is OK?

nandland Whether it will be one video or several does not really matter as long as they are out there, because these type of videos will be watched for years to come (heck just yesterday I watched TI training video from 2011 I think!), it's just the presence of practical part is very important as it allows one to play around with it to better understand how it works. There is a reason all professional training courses always contain lab section.

But that is of course just my humble opinion, you're free to structure your videos however you see fit.

Thanks very much for your reply. I'll work on this.

That was perfect. Love your videos! 😌 very informative and you have a talent for teaching.

Great video. I had to sketch out a simple diagram of simple FIFO just to get a feel and visualize the VHDL design. I can see why you added the r_read_index and r_write_index. Great video even though you made it two years ago.

Stack = first in , first out

Hello! First of all great video! Do you have any example code on how to program a FIFO in Verilog? Thank you!

7:35 unrecoverable error what means? Just failure of program? Or FPGA burned? :D just curious

Real fun starts in FIFO.

Being that the title is "What is a FIFO in an FPGA" is any of this actually specific to an FPGA? I have not yet made it al the way through (and don't have time at the moment), but so far this seems like a great reference video for anyone using FIFOs!

Nice video! Do you have any idea about labview fpga. They have very easy way of programming fpga to understand this kind of topics.

great video! i am about to build a fifo with registers for my behavioral verilog class and I am excited to do this! such an interesting thing to build with hardware XD

Very Informative , Thanks

Thanks again Russel for an amazing video!! Learnt a lot!!

Thanks for this really helpful video

really appreciate you explanation! awesome!

Excellent explanation! Short and relevant. Thanks!

Nandland channel gets basic stuff wrong. Sorry.

Care to elaborate on what, for those of us learning?

List out advantages and disadvantages of fifo

Thanks for uploading :)

Hi Russel, I'd be interested in a video showing how to implement a fifo in BRAM for the ICE40. What do you think?

This will be the next video that I do.

Hi sir,can u pls help in writing algorithm and flow chart..:))

So useful videos! Thank you very much!

thank you sir !

from 12:00 to 15:00 refer

Great video!!

Nice video

Thanks!!

Thanks!

Nice!

great tutorial

great

Nice video dude!

Thanks :)

1. how to calculate the depth of FIFO?

2. what do you mean by BURST?

1. You set it yourself, it can be as deep as you like.

2. Burst just means a lot of data on back-to-back clock cycles with no delays in between.