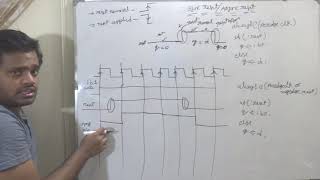

Synchronous Reset Asynchronous Reset in Sequential design with verilog code

HTML-код

- Опубликовано: 5 сен 2024

- Synchronous and Asynchronous Reset is a very important concept for interviews of VLSI jobs.

Clock and reset are synchronous in Synchronous Reset design and reset us Not in sync with clock in asynchronous design.

this video clearly explains the concept with example verilog code and waveform for Synchronous and asynchronous reset using d flipflop.

Follow @exploreelectronics for Basics

👉 Digital Electronics : • Digital Electronics

👉 Verilog HDL Basics : • Verilog HDL

👉 CMOS VLSI Design : • VLSI Design

👉 Whatsapp Channel : whatsapp.com/c...

👉 Telegram : t.me/explore_e...

#synchronous #asynchronous #reset #clock #sequential #vlsijobs #rtl #interview

Very Important for the interview! SUBSCRIBE FOR MORE!

0:30 Differences between sync and async reset

2:24 Verilog code

Awesome explanation sir

Please make videos on how to crack interviews also, it will help many freshers who are trying to get in VLSI field

Could you please explain about giving @negedge clk and @posedgeclk in the testbench for reset