Dynamic Random Access Memory (DRAM). Part 6: Burst Mode and Bank Interleaving

HTML-код

- Опубликовано: 10 сен 2024

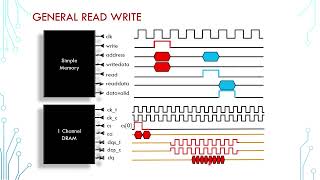

- This is the sixth in a series of computer science videos is about the fundamental principles of Dynamic Random Access Memory, DRAM, and the essential concepts of DRAM operation. This video develops the concepts of dual channel mode and quad channel mode that were introduced in a previous video. It then explains how the operating speed of a DIMM can be greatly increased by outputting a burst of data for a single row and column address, in a technique known as prefetching. The video also introduces a system known as bank interleaving, which greatly reduces the latency of a DRAM array, thereby keeping the data bus fully occupied when transferring cache lines.

THE CONTENTS OF THIS CHANNEL ARE EXTREMELY HELPFUL! I FEEL NOW THAT I CAN BUILD MY OWN RAM IN MY HEAD

Glad you liked it. :)KD

it's hard to understand why such a brilliant channel is so unpopular. thanks a lot for great vids. very useful both for computer science and english. from russia with like!

its not unpopular, its how few people want to learn this stuff or have an aptitude for it

This channel is gold, great job.

Thank you for saying so. :)KD

Thank you for this detailed explanation about the DDR. Outstanding!!!! :)

Thank you for commenting. It makes doing this worthwhile :)KD

Thank you for the series. Here I would like to mention that DIMM is called so not because of 64-bit data line but just because each side is connected to its own electrical lines unlike SIMM having sides of its connector shorted, inheriting SIP package.

The pains which you have taken in explaining the deepest thought with the help of animated diagrams creating the impact directly on the mind.

Please add more vedios on timing and other detailing of DDR, it's a request

Thank you for the useful information. To point out one thing, according to JEDEC standard, DDR4's Burst length is also 8, which is introduced as 16 in the video (8:40). Thank you again for the good video.

You are correct. Burst length in DDR4 is 8, as presented in JEDEC standard docs and (easier do access) DDR4 datasheets from many manufacturers.

Indeed, BL was kept at 8 for DDR4 by introducing Bank Groups, which are also not mentioned.

Tremendous job was done! Many appreciations my friend!

You're very welcome, and thank you :)KD

Thanks for the fantastic content!

8:33 IIUC the burst length of DDR4 is kept at 8n as DDR3, while until DDR5 it becomes 16n.

You're welcome, and thank you :)KD

@@ComputerScienceLessonsAt a time only one memory chip can be active/accessed or multiple memory chips can be active/accessed ?

This is a great channel and much more in-depth than linus tech tips for example

very clear , may be best in youtube for dram

Thank you :)KD

Thank you! Very informative animation.

You're very welcome!

I watch it one by one and my brain in now like a jelly:)

You should take you time. :)KD

6:55 A read, or write, is indeed initiated by the row address. That action triggers an entire row to be read into the row of buffers, using the sense amps. But this is an entirely separate command to the dram. The column address is then LATER sent to read or write a burst of dram words somewhere within that row. The video gives the impression that a read is initiated by BOTH the row and column. Once the slow row opening command is complete, the column read or write command can be sent, acting on a portion of the row buffers. And more than one burst read or write command can be done to different columns of the same open row before that row gets closed out and written back to the correct row within the array so a new row can be opened for R/W.

Reading a 2nd cache line that is from the same row as a first can be done with lower latency because the row does not need to be sensed and stored into the bank’s row buffers. Once a row has been opened, bursts of reads and writes within that row can be initiated one right after the other, without incurring the delay to open a row (tho, a write must wait for the for the delayed burst of data from a previous read to finish on the data bus before a write burst can be sent to the dram).

The point is, the row and column addresses are provided at separate times and in separate commands.

A prior video discusses this

your lesson is sooooo useful!! veryyyyy thank you!!

Delighted to help :)KD

6:35 i finnaly understand arrays.

Excellent. Glad to help. At the risk of muddying the water, you might like this video ruclips.net/video/oWM7fjaiWw0/видео.html :)KD

@@ComputerScienceLessons thank you! 🥹

Hi, can you pls advise some good books on this topic?

thank you sir

At a time only one memory chip can be active or multiple memory chips can be active ?

So In the Bank Interleaving, We get the 64-bit of data from only 8 of the banks in a single chip?

What I don't understand is that the illustration shows that each chip in a rank puts out 8 bits, but later you show that one bank also puts out 8 bits. I guess the bank interleaving part implies that only one bank at a time can output data from one chip. But I'm not sure if this is correct since this is not clear to me.

That is correct. Only one bank on the chip can output data at any one time. Bank interleaving ensures that the banks deliver their data in close succession. If a bank delivers 8 bits, the chip delivers 8 bits. :)KD

how single channel mode can be accessed by the memory controller??

On what parameter is the burst cycle dependent on. Does the size of the data I/O buffer play a role in the burst cycle time

The videos are very good and very interesting to understand. Are you planning to provide more videos on ddr ?

Does a second Rank on one DIMM behave like a second single-rank DIMM in the same channel? Why would a second rank result in more performance?

Aren't rams nowadays byte addressable? Instead of fetching 64 bits, it should be 8, no?

I just got confused while trying to get the defference between prefetching and burst. Happens one of these automatically?

Nonetheless, this series about DRAM is superior!

Why don’t we output 8 bits per array?